Ansys Semiconductor solutions empower engineers to model and optimize every stage of chip development — from process and device physics to system-level validation. With tools for power and signal integrity, electrothermal coupling, stress analysis, and reliability prediction, Ansys enables robust semiconductor innovation. Whether ensuring thermal-aware IC packaging or validating EMI/EMC compliance, it provides a unified platform for faster, more reliable electronics development.

Core Products

Exalto – Interconnect Parasitic Extraction and Analysis

Headline:

High-accuracy interconnect modeling for advanced IC and package designs.

Overview:

Exalto delivers fast and precise parasitic extraction for on-chip interconnects, 3D packaging, and advanced node designs. It accurately captures RLC parasitics across complex metal layers, ensuring signal integrity and timing reliability in high-speed circuits. Exalto integrates seamlessly with Ansys RedHawk-SC and PathFinder-SC for comprehensive power, EM, and ESD verification.

Used for:

IC designers, signal integrity engineers, and packaging specialists working on high-speed or advanced semiconductor nodes.

Key Benefit:

Ensures accurate parasitic modeling early in the design stage, improving performance prediction, reducing re-spins, and supporting signoff-grade accuracy.

PathFinder SC – Full-Chip ESD and EOS Reliability Analysis

Headline:

Advanced ESD and electrical overstress verification for modern SoC designs.

Overview:

PathFinder-SC provides complete-chip ESD protection and reliability verification in a scalable cloud-native platform. It analyzes ESD discharge paths, current density, and potential EOS risks across entire ICs, ensuring compliance with foundry reliability standards. The tool integrates seamlessly with RedHawk-SC and Exalto for a unified reliability signoff flow.

Used for:

IC reliability engineers and design verification teams focusing on ESD/EOS robustness.

Key Benefit:

Prevents costly ESD-induced failures with full-chip visibility, automated rule checks, and high scalability for the latest semiconductor technologies.

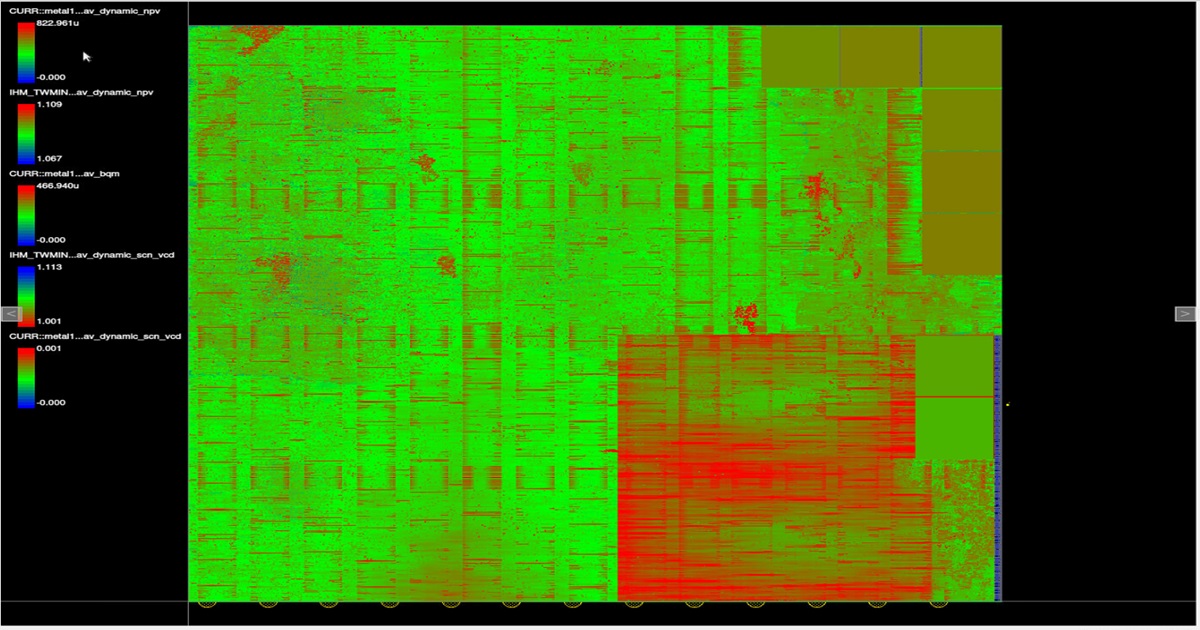

Red Hawk SC – Power Integrity and Reliability Signoff

Headline:

Industry-standard solution for full-chip power, EM, and thermal integrity analysis.

Overview:

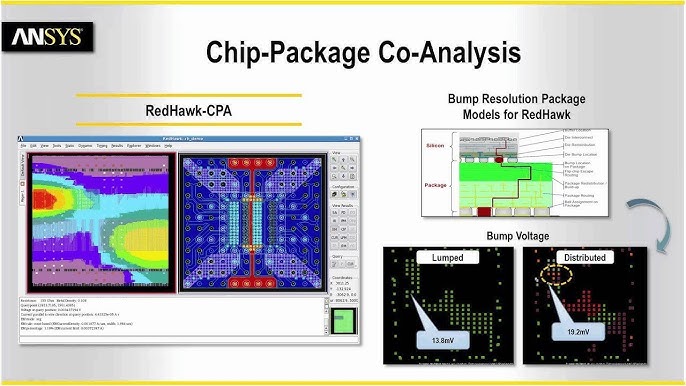

RedHawk-SC delivers signoff-level power integrity, IR drop, and electromigration (EM) analysis for modern SoC designs. Built on a scalable cloud-native architecture, it enables designers to simulate massive designs efficiently and accurately. It supports dynamic voltage drop analysis, thermal coupling effects, and integration with PathFinder-SC and Exalto for complete reliability coverage.

Used for:

SoC designers, power integrity engineers, and chip signoff teams.

Key Benefit:

Accelerates reliable chip delivery with proven accuracy, cloud scalability, and complete coverage for power, EM, and thermal verification.

RaptorH – Fast, Accurate RF and Analog Parasitic Extraction

Headline:

High-performance 3D field solver for RF, analog, and mixed-signal IC layouts.

Overview:

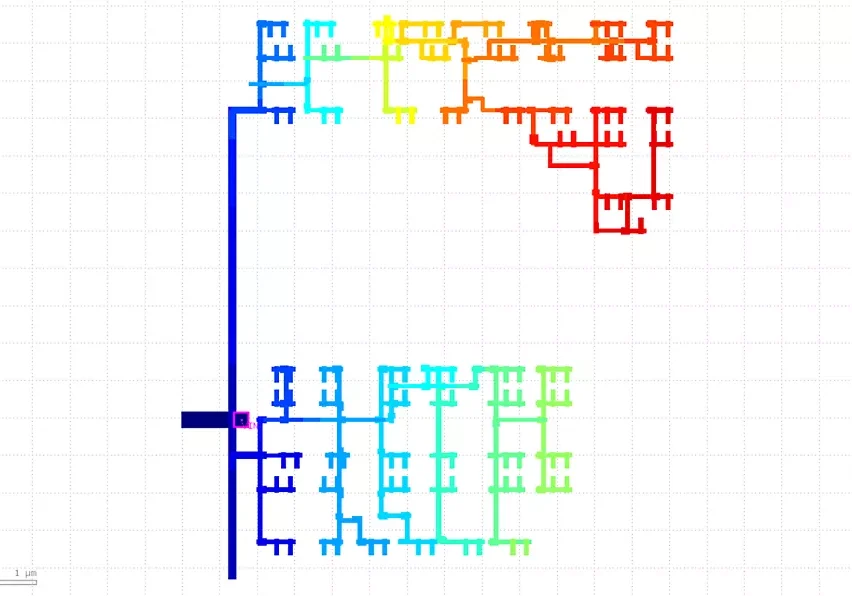

RaptorH combines 3D electromagnetic (EM) accuracy with unmatched speed for parasitic extraction in RF and analog circuits. Its hybrid field solver ensures precise modeling of inductive and capacitive effects, crucial for high-frequency and noise-sensitive designs. The tool integrates with major design platforms for seamless layout-to-signoff workflows.

Used for:

RF, analog, and mixed-signal IC designers require accurate EM parasitic extraction.

Key Benefit:

Delivers near-signoff EM accuracy with up to 10x faster turnaround, enabling confident RF performance prediction and first-pass silicon success.

Clock FX – Power-Aware Clock Network Analysis

Headline:

Comprehensive clock network analysis for performance, power, and reliability optimization.

Overview:

Clock FX provides detailed analysis and optimization of clock tree networks, addressing skew, jitter, latency, and power consumption. It enables designers to visualize and resolve timing bottlenecks while ensuring robust operation across process and temperature variations. Integration with RedHawk-SC allows for power-aware clock analysis and electromigration signoff.

Used for:

Physical design engineers, timing specialists, and chip architects.

Key Benefit:

Improves clock network efficiency and reliability, minimizing timing violations and enabling higher frequency operation with lower power.

Highlights of Semiconductor Simulation

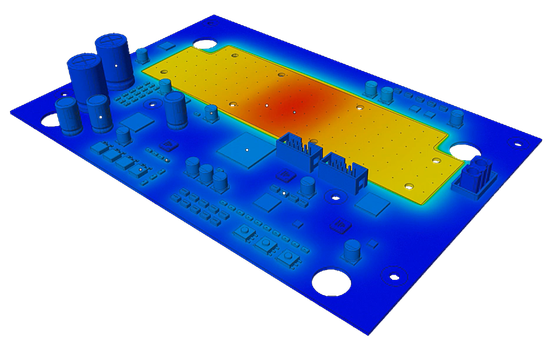

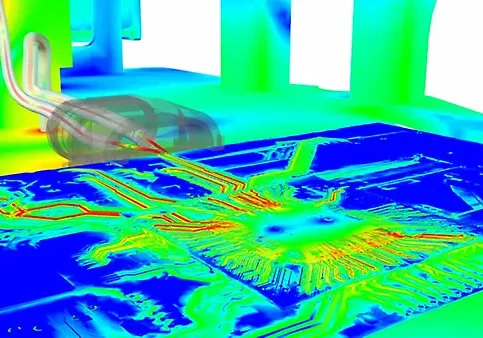

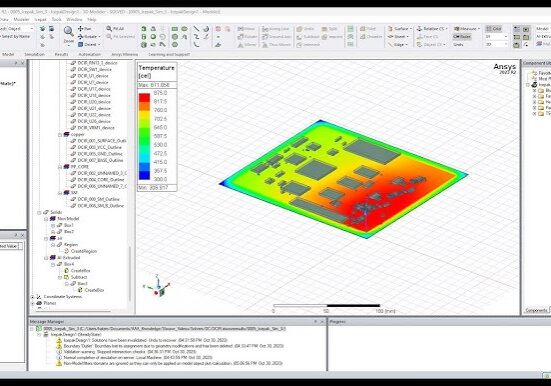

Chip-Level Thermal and Power Integrity Analysis

Gain accurate insights into power density, heat dissipation, and voltage drop across semiconductor designs to ensure stable operation and performance under real workloads.

Key Capabilities

Benefits

Signal and Electromagnetic Integrity

Ensure high-speed signal reliability and EMI/ESD robustness across interconnects, packages, and SoC architectures.

Key Capabilities

Benefits

Power Analysis and Optimization

Optimize dynamic and static power consumption to improve efficiency and reduce leakage across RTL and gate-level designs.

Key Capabilities

Benefits

Clock Network Design and Jitter Analysis

Analyze and optimize clock tree performance for low skew, minimal jitter, and high timing stability.

Key Capabilities

Benefits

Parasitic Extraction and Layout Verification

Perform advanced parasitic extraction for analog, RF, and mixed-signal designs to ensure layout accuracy and performance correlation.

Key Capabilities

Benefits

Applications Across Industries

Semiconductor simulations play a key role in electronics, telecommunications, automotive, aerospace, and consumer device industries — from chip design to thermal reliability.

At SolidTrust Technologies, we adapt Ansys Semiconductor solutions to enable faster innovation, efficient power management, and long-term reliability.

Relevant FAQs

Yes, Ansys Semiconductor tools accurately predict chip temperature, power density, and electrical performance.

Absolutely, you can analyze thermal-mechanical and thermo-electrical effects for advanced packaging designs.

Yes, Ansys provides PI/SI analysis to ensure reliable power delivery and minimize signal distortion.

Yes, Ansys enables stress, fatigue, and electromigration analysis for long-term reliability prediction.

Yes, you can integrate chip-level models with board and system-level simulations for complete electronic validation.

Yes, Ansys Semiconductor tools support sub-5nm nodes, 3D-ICs, and advanced packaging architectures.

Yes, Ansys allows engineers to predict electrostatic discharge and thermal failure risks accurately.

Success Stories